Verilaror

Verilatorは、1994年にCPUをC言語にて検証するために、VerilogからCへのトランスレータとして開発されたもので、現在でもWilson

Synder氏らによりアクティブに開発が進められています。

Verilatorは、GNU General Public Licenseで公開されているフリーなソフトウェアです。

設計したVerilogモジュールを、SystemCで記述したテストベンチを作成することから、SystemC設計への足がかりとすることができます。

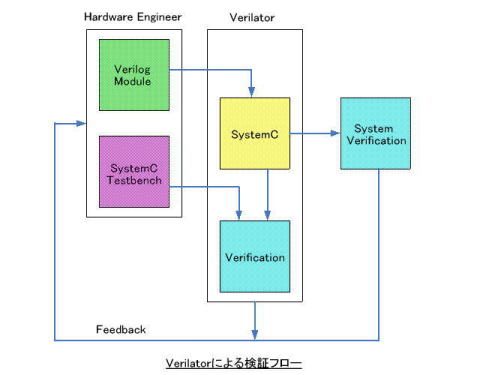

Verilatorによる検証フロー

ハードウェアエンジニアは、Verilog モジュールと、SystemCで記述されたテストベンチを作成すれば、Verilatorを使って高速なシミュレーションができます。

Verilatorで変換されたSystemC,C++は、システム検証に使うことができます。

Verilatorを使うメリット

シミュレーションが高速に行われる。

Verilog Simulator Benchmarks

Verilatorにより変換したSystemC、C++モジュールを、システム検証に使える。

SystemCによるテストベンチ作成により、SystemCによる設計移行への足がかりとなる。

フリーソフトウェアである。

Verilatorを使うデメリット

インストールが難しい。

詳しい操作マニュアルがない。

無保証である

Example

Verilatorは、GNU General Public Licenseで公開されているフリーなソフトウェアです。

設計したVerilogモジュールを、SystemCで記述したテストベンチを作成することから、SystemC設計への足がかりとすることができます。

Verilatorによる検証フロー

ハードウェアエンジニアは、Verilog モジュールと、SystemCで記述されたテストベンチを作成すれば、Verilatorを使って高速なシミュレーションができます。

Verilatorで変換されたSystemC,C++は、システム検証に使うことができます。

|

Verilatorを使うメリット

シミュレーションが高速に行われる。

Verilog Simulator Benchmarks

Verilatorにより変換したSystemC、C++モジュールを、システム検証に使える。

SystemCによるテストベンチ作成により、SystemCによる設計移行への足がかりとなる。

フリーソフトウェアである。

Verilatorを使うデメリット

インストールが難しい。

詳しい操作マニュアルがない。

無保証である

Example

この改行は必要→